a.主要应用:高功耗处理器,军事用芯片

b.主要分为:

1.Flip-Chip

2.BondWire

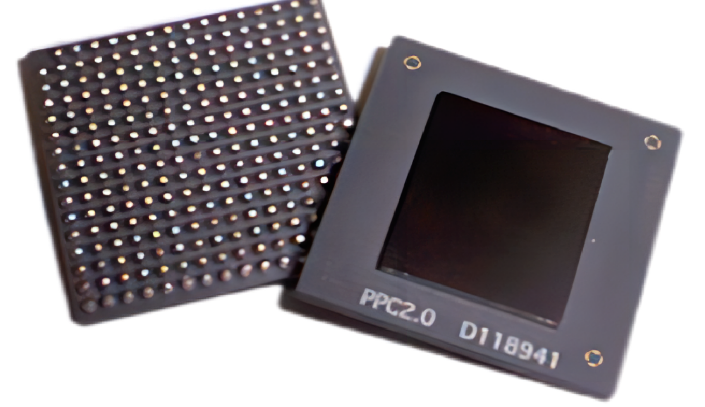

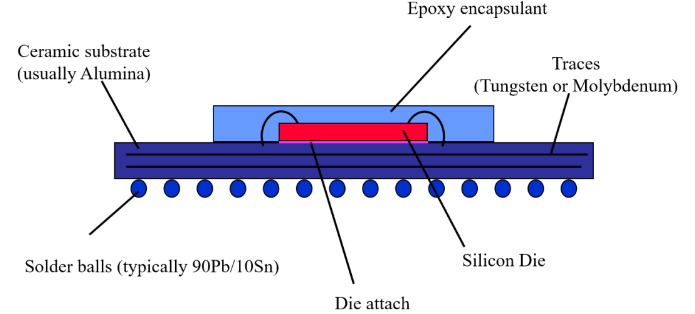

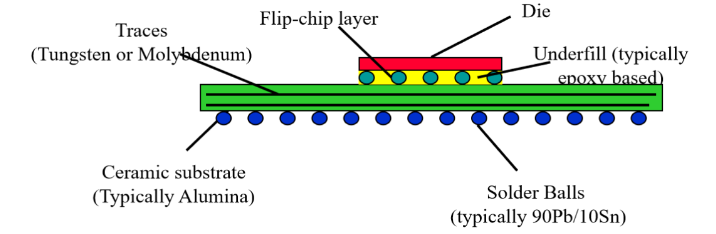

主要类型的CBGA封装

Wire-Bonded CBGA

Flip-Chip CBGA

Bare-Die

Caped

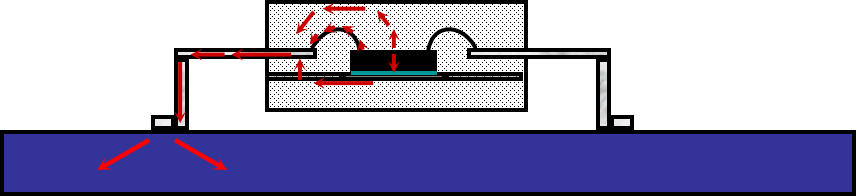

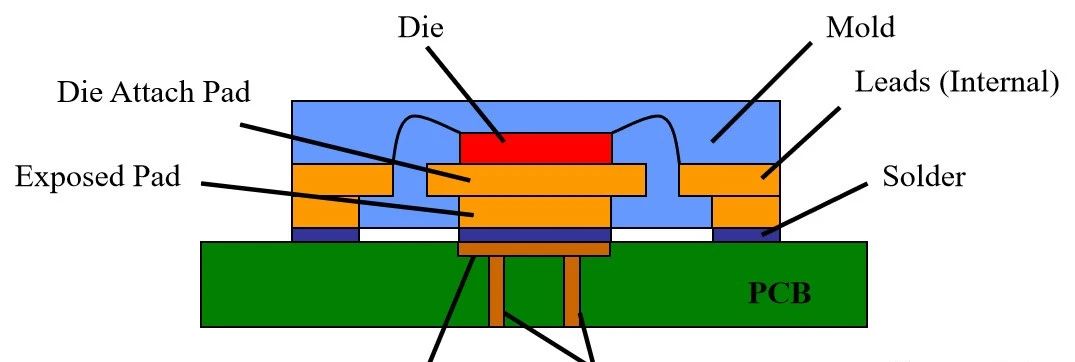

截面结构图

注意:在Lead数目较多的情况下,Bondwires的传热分额可能高达15%,但是在热测试芯片中,由于Bondwires数目较少,忽略了这部分热量

注意:一部分热量由芯片传至散热器上,又有可能重新传递回芯片上.

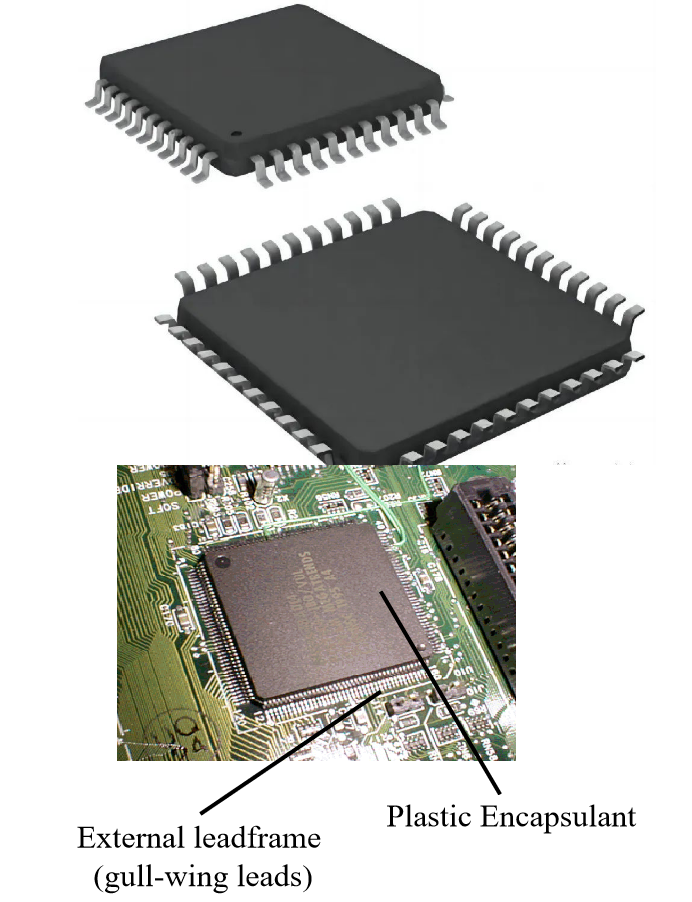

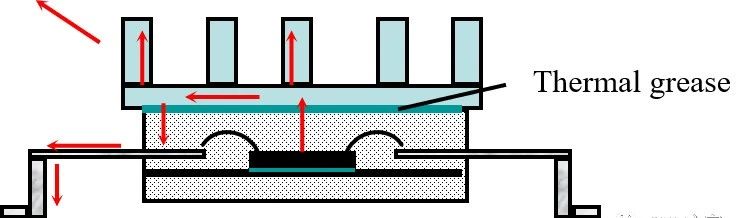

SOP/TSOP封装模型的建立

a.Small Outline Package

b.Low profile version known as Thin Small Outline Package (TSOP)

c.类似于 PQFP, 只是只有两边有管脚

d.广泛应用于内存芯片

e.常见的类型

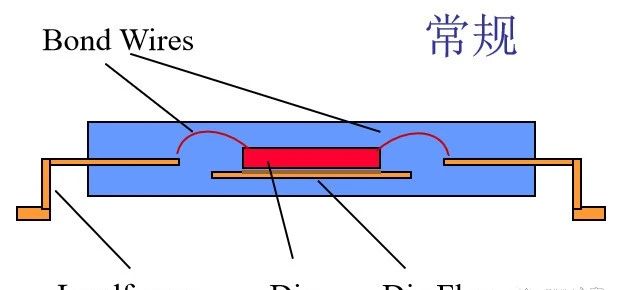

1.常规

2.Lead-on-Chip

![]()

![]()

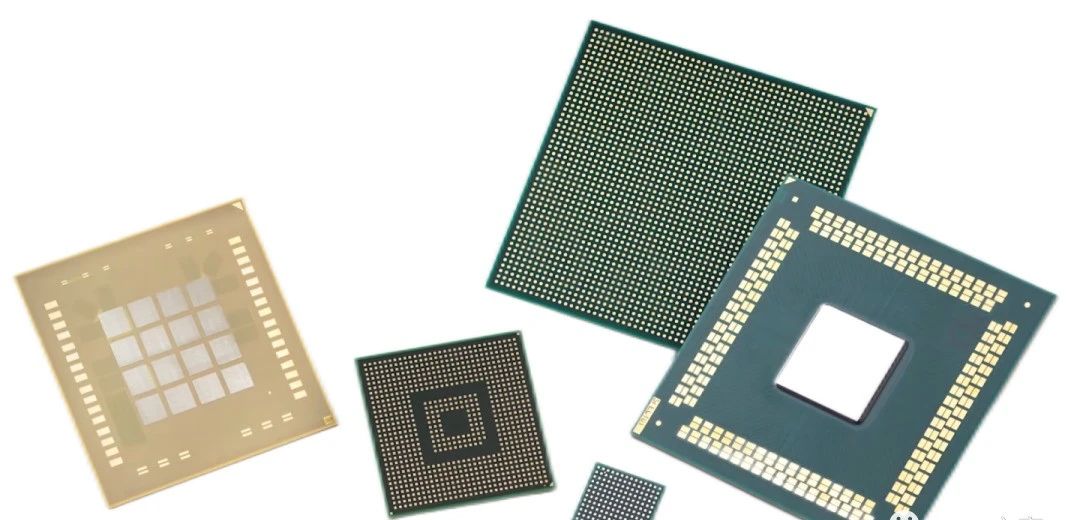

Micro-BGATM封装模型的建立

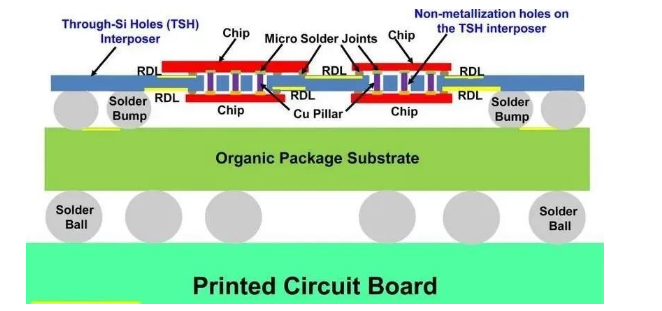

mZ-Ball Stack TM

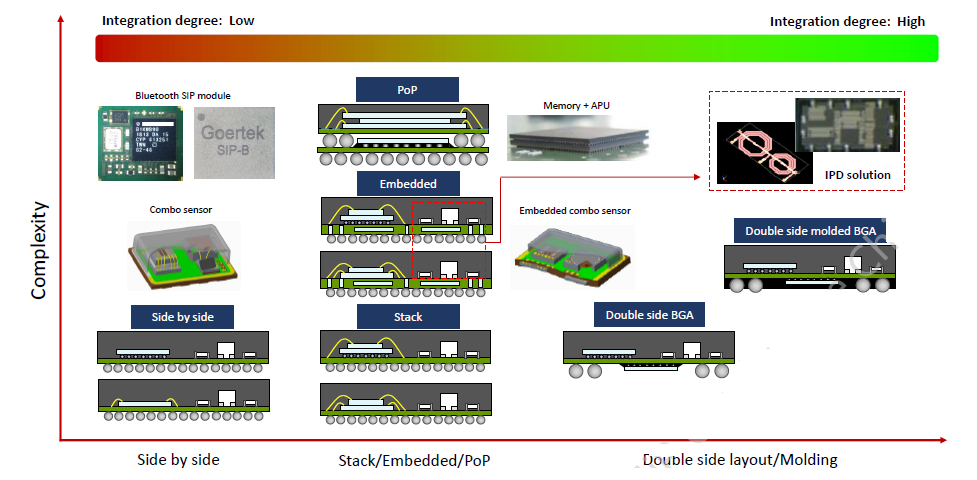

日前行业和市场最火的工艺

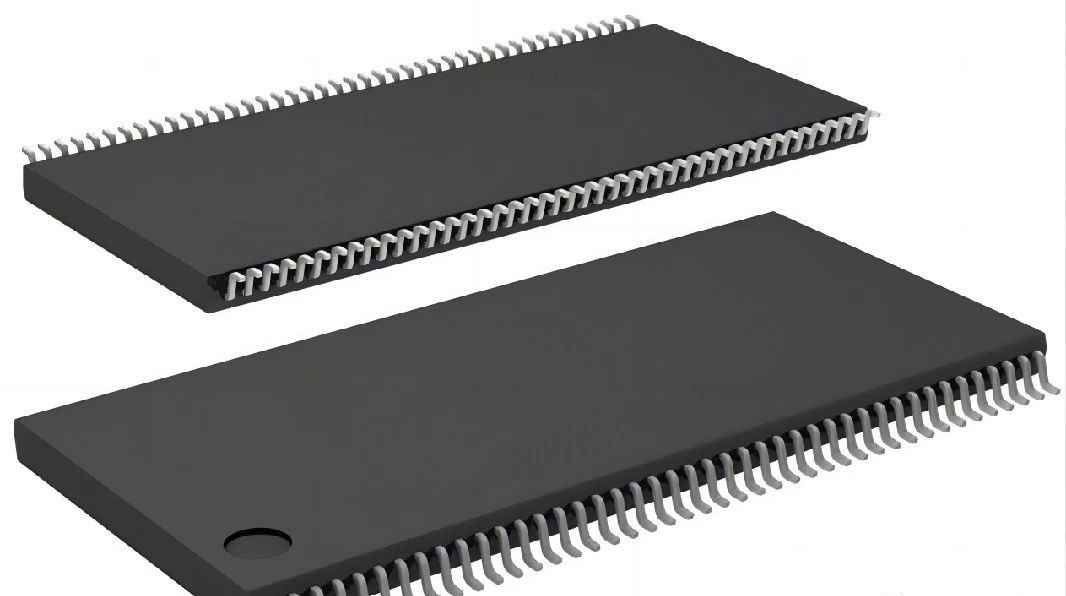

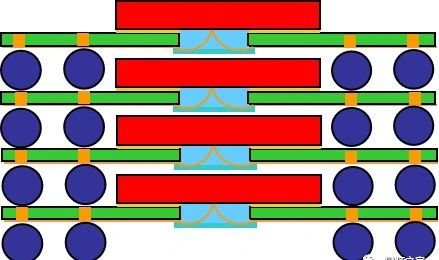

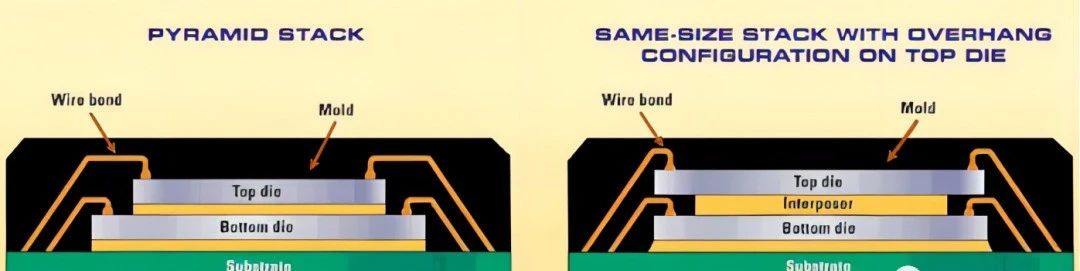

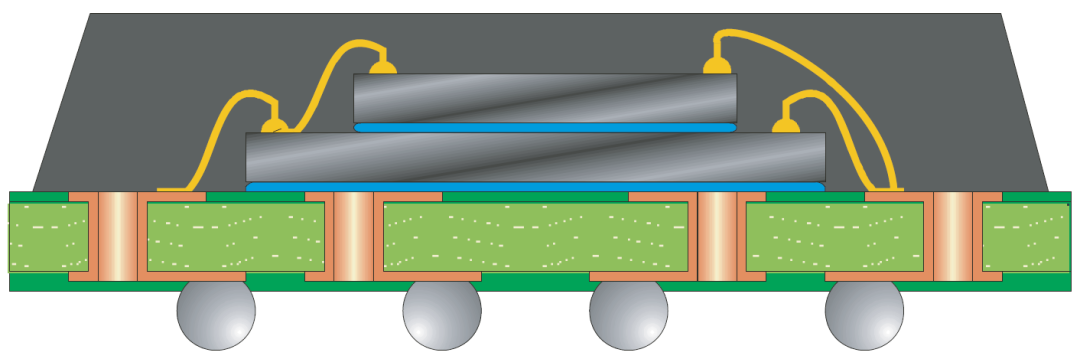

堆栈裸片封装(Stacked-Die Packages)的建模

a.别名 SiP (System in Package)

b.通常堆栈2-4层裸片

1.目前也在研发6层或更多数目的堆栈裸片

2.当所有的功能难以集中在单片裸片中时应用

c.常见的应用:

Flash/SRAM,ASIC/Memory,Memory/Logic,Analog/Logic

d.In area array or leaded package outlines

e.加工困难,第层裸片都必须加工为特别薄 (50微米级)

f.需要精细的电路设计和散热设计

g.尚无成熟的热简化模型

h.芯片常用于体积要求较小的手机或其它移动电子设计

SiP

基于打线的3D-SIP封装技术

免责声明:本文系网络转载或改编,版权归原作者所有。但因转载众多,无法确认真正原始作者,故标明转载来源。如涉及版权等问题,

请与我们联系删除!本文内容为原作者观点,并不代表我司赞同其观点和对真实性负责。